新闻中心

PCB单面板打样设计流程

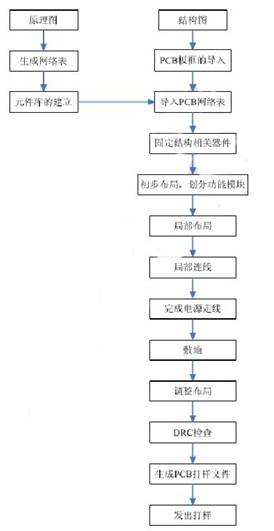

单面板打样的设计流程:

右图为一个大致的PCB设计步骤,具体设计可能会与此有部分出入。

1、 准备部分:

在开始进行PCB布局时,首先应当完成原理图设计,得到一个正确的原理图,这是单面板打样设计的基础。通过原理图我们可以得到一个各个器件连接属性的网络表,此外,根据器件的参数,我们可以找到相关的元器件资料并建立所有元器件的封装。 此外,还需要结构部配合给出板框尺寸以及各个安装位置,功能借口的位置。

2、 在完成准备工作后,进入具体操作部分,但首先需要将所有封装文件及网络表导入到建立好外框的PCB文件中。导入过程中可能会提示一些元件封装错误,请根据错误提示排除错误。

3、 在完成导入文件操作后,首先第一步要做的是固定结构相关器件,如LED,按键,卡座,液晶,红外发射器等。将这些器件移动到对应的安装位置,并在属性里选择锁定,防止误操作。

4、 在确立的优先器件后,我们可以进行大致布局,大致布局的目的是决定各个功能模块的位置,在PCB设计中,一般默认为:

A、 除需要安装到表面的器件外,所有贴片器件放置到插件器件的一面,一般为底层;

B、 计量单元放置在左下角,方便进线;

C、 MCU放置在LCD背面,并且做到引线足够短;

D、 接口部分放置到PCB右下角,方便出线;

E、 变压器远离互感器和锰铜分流器等对漏磁较敏感的器件;

F、 需要隔离的电路之间保留足够的爬电距离;

5、 在完成了大致布局后,可以进行局部布局。完成各个功能模块对应器件的摆放。在局部布局时需要考虑的因素有:

A、 晶振应当尽量靠近晶振管脚,做到走线尽量短;

B、 去耦电容应当尽量靠经IC的电源输入脚;

C、 IC之间有高速连接的器件应当尽量靠近;

D、 要考虑维修的方便性,对一些器件的摆放位置作出优化,以免造成生产困难;

E、 留一定的板边距,要求边距最好做到4mm以上,否则在SMT车间易造成贴片时贴片取料头意外损坏,在波峰焊接时造成器件与链条碰撞,无法一次性用波峰焊接完成插件焊接,需要安排更多工位补焊;

F、 压敏电阻、聚酯电容、瞬态抑制二极管和稳压管,滤波电容应当放到需要保护器件的前端;

G、 注意高压的和低压信号的距离。

6、 在完成了局部布局后,可以进行元器件的连线。连线需要注意以下方面:

A、 了解各个器件可能流过的电流大小以及最大的冲击电流大小,能够大致了解走线上承载的信号对其他信号可能的影响。以便进行走线粗细的设置

B、 高压信号到压敏电阻和聚酯电容两端的走线应当尽量采用较宽的线宽,使保护器件能够及时地释放过载能量,同时还能防止线路被瞬间大电流烧毁;

C、 低电压供电信号主线路走线采用36mil,减少导线电阻,在芯片附近可以采用24mil及以下宽度。

D、 小信号连线可以采用10mil或者12mil,太细会造成废板率过高,太粗没有意义。

E、 高频信号附近不能走线,例如晶振底部;

F、 尽量减少过孔的连接。 走线的质量直接影响到PCB板的性能,在实际布线时可能需要推翻重来,甚至回到原理图修改IO口定义。这是最为费时的部分。

7、 在完成所有信号线的走线后,可以进行电源线的走线,电源线的走线应当保证足够的宽度,避免线宽的突变以及直角的拐角。此外不能把电源线形成一个环路。

8、 在完成线路连接后,可以进行铺地的处理,形成一个大的接地平面,同时等效于完成地线的布线。

9、 在完成了地平面后,可以以此为参照,以接地面积最大化为目标进行器件布局的调整,在调整时要防止大片的接地只通过几个过孔与主地相连接。要注意芯片下的铺地完整性。此外还能较好的观察布线和器件摆放得美观性,还有各个信号的回流环路是否完整。在此步骤时,完成所有器件标示的调整和修改,并打上公司Logo和PCB版本号。

10、 DRC校验是一个高效可靠的检查工具,它可以根据我们设定的规则可靠的检查所有PCB板的绘制规范,同时指出错误并以高亮标识错误。

11、 在确认所有设计无误后,可以将PCB板导出,导出格式为Protel PCB 2.8 ASCII File。

12、 最后由文控发出打样。

由于有些公司PCB板需求量很大,每次设计,打样,焊接,调试的时间累计起来通常要10天左右,当发现PCB由于低级错误而需要重新绘制时,会耗费大量的时间,因此成功率很重要选择有实力的供应商也非常的重要,为了方便需求量大的客户,我司推广出了24小时打样,72小时打样服务,欢迎来电洽谈业务!